Performance enhancement of flipped voltage follower current mirror in nanoscale technology

Authors

Abstract

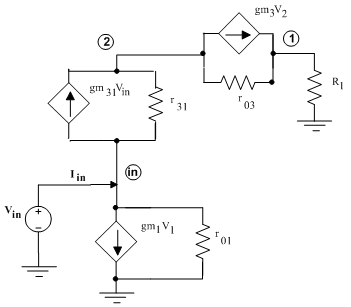

The trend of technology downscaling to accommodate low supply requirement has been a continuous motivation for the IC industry. The nanoscale dimension MOSFET demands low supply but at the same time results in poor performance of analog circuits due to MOSFET secondary effects. In this paper, a fundamental block of current mode circuit, current mirror is proposed designed using MOSFET in nanoscale technology. The performance enhancement is done using modified structure of recently reported low voltage cell, flipped voltage follower. The modification incorporates cascoding of self cascode stage in flipped voltage follower. Further enhancement of this configuration is done in terms of MOSFET operating region for which quasi-floating gate technique is adopted. As a result, the final proposed quasi-floating gate based flipped voltage follower structure results is extremely low impedance at its output node compared to conventional flipped voltage follower. This property helps to achieve the ideal requirement of current mirror’s input resistance. For output resistance the regulated cascode super cascode modified again with quasi-floating gate technique is used. The proposed current mirror results in input resistance of 81 ohms have been showed output resistance of 112 giga ohms & bandwidth of 2.8 giga hertz. The proposed circuit is designed using MOS technology of 180 nanometer & analyzed using Spice simulator at a dual polarity supply of 0.5 volt.

Graphical Abstract

Keywords

References

[1] Akbari M., Javid A., Hashemipour O., (2014), A high input dynamic range, low voltage cascode current mirror and enhanced phase-margin folded cascode amplifier. 22nd Iran. Conf. Elect. Eng. (ICEE). 77-81. https://doi.org/10.1109/IranianCEE.2014.6999507

[2] Carvajal R. G., Ramirez-Angulo J., Lopez-Martin A. J., Torralba A., Galan J. A. G., Carlosena A., Chavero F. M., (2005), The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Transact. Circuits and Systems I: Regular Papers. 52: 1276-1291. https://doi.org/10.1109/TCSI.2005.851387

[3] Raj N., Singh A. K., Gupta A. K., (2015), Low power circuit design techniques: A survey. Int. J. Computer Theory and Eng. 7: 172-176. https://doi.org/10.7763/IJCTE.2015.V7.951

[4] Prodanov V. I., Green, M. M., (1996), CMOS current mirrors with reduced input and output voltage requirements. Inst. Eng. Technol. Electron. Lett. 32: 104-108. https://doi.org/10.1049/el:19960076

[5] Torralba A., Carvajal R. G., Muñoz F., Ramirez-Angulo J., (2003), New output stage for low supply voltage, high-performance CMOS current mirrors. In Proceed. 2003 Int. Symp. Circuits and Systems. 1: I-I. https://doi.org/10.1109/ISCAS.2003.1205552

[6] Raj N., Singh A. K., Gupta A. K., (2014), Low power high output impedance high bandwidth QFGMOS current mirror. Microelectron. J. 45: 1132-1142. https://doi.org/10.1016/j.mejo.2014.05.005

[7] Esparza-Alfaro F., Lopez-Martin A. J., Carvajal R. G., Ramirez-Angulo J., (2014), Highly linear micropower class AB current mirrors using Quasi-Floating Gate transistors. Microelect. J. 45: 1261-1267. https://doi.org/10.1016/j.mejo.2014.02.006

[8] Raj N., Singh A. K., Gupta A. K., (2014), Low voltage bulk driven self biased cascode current mirror with bandwidth enhancement. Electron. Lett. 50: 23-25. https://doi.org/10.1049/el.2013.3600

[9] Raj N., Singh A. K., Gupta, A. K., (2016), Low voltage high output impedance bulk-driven quasi-floating gate self-biased high-swing cascode current mirror. Circuits, Systems, and Signal Process. 35: 2683-2703. https://doi.org/10.1007/s00034-015-0184-4

[10] Domala N., Sasikala G., (2022), Low voltage quasi floating gate current mirror with improved output impedance. Int. J. Public Sector Perform. Manag. 10: 499-512. https://dx.doi.org/10.1504/IJPSPM.2022.126404

[11] Raj N., Singh A. K., Gupta, A. K., (2016), Low voltage high performance bulk driven quasi-floating gate based self-biased cascode current mirror. Microelectron. J. 52: 124-133. https://doi.org/10.1016/j.mejo.2016.04.001

[12] Safari L., Minaei S., (2017), A low-voltage low-power resistor-based current mirror and its applications. J. Circuits, Systems and Comput. 26: 1750180. https://doi.org/10.1142/S0218126617501808

[13] Doreyatim M., Akbari M., Nazari M., Mahani S., (2019), A low-voltage gain boosting-based current mirror with high input/output dynamic range. Microelectron. J. 90: 88-95. https://doi.org/10.1016/j.mejo.2019.05.022

[14] Bchir M., Aloui I., Hassen N., (2020), A bulk-driven quasi-floating gate FVF current mirror for low voltage, low power applications. Integration. 74: 45-54. https://doi.org/10.1016/j.vlsi.2020.04.002

[15] Shrivastava A., Pandey R., Jindal C., (2020), Low-voltage flipped voltage follower cell based current mirrors for high frequency applications. Wireless Pers. Communic. 111: 143-161. https://doi.org/10.1007/s11277-019-06849-2

[16] Raj N., (2021), Low voltage FVF current mirror with high bandwidth and low input impedance. Iran. J. Electric. Electron. Eng. 17: 1972-1972. https://doi.org/10.22068/IJEEE.17.3.1972

[17] Domala N., Sasikala G., (2021), Low power flipped voltage follower current mirror with improved input output impedances. Sādhanā. 46: 1-11. https://doi.org/10.1007/s12046-021-01665-6

[18] Raj N., (2021), Low-voltage wide-range high-impedance flipped voltage follower current mirror. Sādhanā. 46: 171-176. https://doi.org/10.1007/s12046-021-01694-1

[19] Anil P., Tamil S., Raj N., (2021), Design of low voltage quasi-floating self cascode current mirror. U. Porto J. Eng. 7: 33-45. https://doi.org/10.24840/2183-6493_007.004_0003

[20] Kumar P. A., Tamil S., Raj N., (2021), Low voltage improved impedance wide bandwidth current mirror. Int. J. Inform. Technol. 13: 2411-2417. https://doi.org/10.1007/s41870-021-00785-w

[21] Domala N., Sasikala G., Raj N., (2023), Low voltage high bandwidth FVF current mirror using quasi floating self-cascode output stage. Analog Integ. Circ. Signal Process. 1-13. https://doi.org/10.1007/s10470-023-02205-4

[22] Karimi Pashaki Y., Sedigh Ziabari S. A., Eskandarian A., Rahnamaei A., (2023), Numerical optimization of threshold voltage and off-current of a nano-scale symmetric double gate MOSFET based on the genetic algorithm: Various strategies compatible with device applications. Int. J. Nano Dimens. 14: 91-102. https://doi.org/10.22034/ijnd.2022.1963798.2166

[23] Ruhil Sh., Khanna V., Dutta U., Shukla N. K., (2021), A study of emerging semi-conductor devices for memory applications. Int. J. Nano Dimens.12: 186-202. https://doi.org/10.22034/ijnd.2021.680122

[24] Tayal Sh., Samrat P., Keerthi V., Jena B., Rajendra K., (2021), Conventional vs. junctionless gate-stack DG-MOSFET based CMOS inverter. Int. J. Nano Dimens. 12: 98-103. https://doi.org/10.22034/ijnd.2021.677807

[25] Rahnamaei A., Zare Fatin G., Eskandarian A., (2019), Design of a low power high speed 4-2 compressor using CNTFET 32 nm technology for parallel multipliers. Int. J. Nano Dimens. 10: 114-124.

[26] Khorramrouz F., Sedigh Ziabari S. A., Heydari A., (2018), Analysis and study of geometrical variability on the performance of junctionless tunneling field effect transistors: Advantage or deficiency. Int. J. Nano Dimens. 9: 260-272.