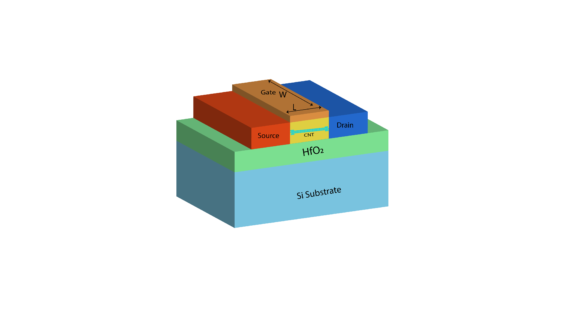

Design of Binary-to-Quaternary Converters based on CNTFET Transistors

Authors

Abstract

In order to connect two binary and quaternary systems, it is necessary to use binary-to-quaternary (B2Q) and quaternary-to-binary (Q2B) converters. These converters convert numbers from logic 2 to 4 and vice versa. In this paper, we designed a new binary-to-quaternary converter circuit using CNT transistors. In this circuit, the Power Delay Product (PDP) has been reduced to14.59% and 15.39% compared to best previous works. Also, this circuit has better driving ability and temperature stability than best previous works. The simulation results using Stanford’s 32 nm CNTFET model in HSPICE software are at a voltage of 0.9 V.

Graphical Abstract

Keywords

References

[1] P.C. Balla, A. Antoniou, “Low power dissipation MOS ternary logic family,” IEEE J. Solid-State Circuits, 19, (5), pp. 739–749,1984.

[2] Mo. Yoosefi Nejad, M. Mosleh “A Review on QCA Multiplexer Designs,” Majlesi Journal of Electrical Engineering, Vol. 11, (5), no.2, 2017.

[3] M. Mishra, S.H. Akashe, “High performance, low power 200 Gb/s 4:1 MUX with TGLin 45 nmtechnology,” Appl. Nanosci, 2014.

[4] P. Avouris, J. Appenzeller, R. Martel, S.J. Wind, “Carbon nanotube electronics,” IEEE Proc, 91, pp.1772–1784, 2003.

[5] S. Lin, Y. Kim, F. Lombardi, “CNTFET-based design of ternary logic gates and arithmetic circuits,” IEEE Trans. Nanotechnol, Vol. 10, No. 2, pp. 217–225, 2011.

[6] S. V. RatanKumar, L. Koteswara Rao and M. Kiran Kumar, “Design of Ternary Logic Circuits using Pseudo N-type CNTFETs,” ECS Journal of Solid State Science and Technology, 2022.

[7] M. Shahangian, S.A. Hosseini, R. Faghih Mirzaee “A Universal Method for Designing Multi-Digit Ternary to Binary Converter Using CNTFET,” Journal of Circuits, Systems, and Computers. 2020.

[8] Bolourforoush, M. Mohammadi Ghanatghestani, “A New Quaternary Full Adder Cell based on CNFET for Use in Fast Arithmetic Circuits,” ECS J. Solid State Sci. Technol., 11, 9, 2022.

[9] Daraei, S.A. Hosseini, “Novel energy-efficient and high-noise margin quaternary circuits in nanoelectronics,” AEU Int. J. Electron. Commun, 105, 145–162, 2019.

[10] E. Roosta, S.A. Hosseini, “A novel multiplexer-based quaternary full adder in nanoelectronics,” Circuits Syst. Signal Process, 38, pp. 4056–4078, 2019.

[11] E. Shahrom, S.A. Hosseini, “A new low power multiplexer based ternary multiplier using CNTFETs,” AEU Int. J. Electron. Commun, 93, pp. 191–207, 2018.

[12] SH. Gadgil, CH. Vudadha, “Design of CNFET-based Low-Power Ternary Sequential Logic circuits,” IEEE 21st International Conference on Nanotechnology (NANO), 2022.

[13] S. Nemati, M. Haghi Kashani, R. Faghih Mirzaee, “Comprehensive survey of ternary full adders: Statistics, corrections, and assessments,” IET Circuits, Devices& Systems, 2023.

[14] N. Hajizadeh Bastani, M. H. Moaiyeri, K. Navi, “An Energy and Area Efficient Approximate Ternary Adder Based on CNTFET Switching Logic,” Circuits, Sys. Signal Processing, 37, No. 5, pp. 1863-1883, 2018.

[15] K. Rahbari, S.A Hosseini, “Novel ternary D-flip-flap-flop and counter based on successor and predecessor in nanotechnology,” AEU Int. J. Electron. Commun, 109, pp. 107–120, 2019.

[16] S.A. Hosseini, S. Etezadi, “A novel very low-complexity multi-valued logic comparator in nanoelectronics,” Circuits Syst. Signal Process, 39, pp. 223–244, 2020.

[17] J. Appenzeller, “Carbon nanotubes for high-performance electronics - Progress and prospect,” Proc IEEE, 96:201–11, 2008.

[18] P. L. McEuen, M.S. Fuhrer, H. Park, “Single-walled carbon nanotube electronics,” IEEE Transactions on Nanotechnology, pp.78-85, 2002.

[19] J. Deng, H. S.P Wong, “A compact SPICE model for carbon-nanotube field-effect transistors including non-idealities and its application—Part II: full device model and circuit performance benchmarking,” IEEE Trans. Electron. Device, 54(12), 3195–3205, 2007.

[20] S. Rasmita, S. Sahoo, K. Krishna Chaitanya Sankisa, “Design of an efficient CNTFET using optimum number of CNT in channel region for logic gate implementation,”IEEE Conference Publications, pp.1-4, 2015.

[21] S. L.Hurst, “Multiple-valued logic, its status and its future,” IEEE Transactions on computers, 1984.

[22] S.A. Ebrahimi, M. R. Reshadinezhad, A. Bohlooli, M. Shahsavari, “Efficient CNTFET-based design of quaternary logic gates and arithmetic circuit,”Microelectronic Journal, 53, pp.156-166, 2016.

[23] M.Ghelichkhani, S. A.Hosseini, S. H. Pishgar Komleh, “Multi-digit Binary-to-Quaternary and Quaternary-to-Binary Converters and Their Applications in Nanoelectronics,” AEU Int. J. Electron. Commun, 39(4), pp. 1920 - 1942, 2019.

[24] J. Liang, L.Chen,J.Han, F.Lombardi, “Design and evaluation of multiple valued logic gates using pseudon-type carbon nano tube FETs,” IEEETrans.Nano- technol. 695–708,2014.

[25] CNFET Model. http://nano.stanford.edu/models

[26] Kajal, Vijay Kumar Sharma, “An efficient low power method for Fin FET domino OR logic circuit,” Microprocessors and Microsystems, 2022, https://doi.org/10.1016/j.micpro.2022.104719.

[27] M.H. Moaiyeri, A. Doostaregan, K. Navi, “Design of energy-efficient and ternary circuits for nanotechnology,” IET Circ Dev Syst, 5(4):285296, 2011.

[28] T. Sharma, L. Kumre, “Design of low power multi-ternary digit multiplier in CNTFET technology,” Microprocessors and Microsystems, 73, 2020.

[29] R.F. Mirzaee, M.H. Moaiyeri, K. Navi, “Dramatically low-transistor-count high-speed ternary adders,” in: 43rd Int. Symp. On Multi Valued Logic, pp. 170–175, 2013.