Authors

- Computer Department of Computer Engineering, Kerman Branch, Islamic Azad University, Kerman, Iran.

- Department of Computer Engineering, Shahid Bahonar University of Kerman, Kerman, Iran.

Abstract

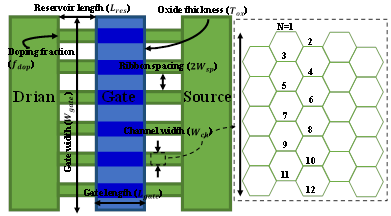

The multiplier circuit is considered to be a significant component of larger circuits, such as the arithmetic and logic unit (ALU), and it is crucial to enhance its energy efficiency. This objective can be easily achieved by utilizing graphene nanoribbon field-effect transistor (GNRFET) devices and adopting ternary logic. Ternary circuit designs demonstrate superior energy efficiency and occupy less space compared to binary ones. The adjustability of the threshold voltage (Vth) in GNRFET devices is directly influenced by the width of the graphene nanoribbon (GNR). This offers significant advantages for ternary circuit designs. This paper presents a 24-transistor low-energy GNRFET-based single-trit ternary multiplier. Our proposed design incorporates an enhanced voltage division technique to achieve logic ‘1’ while minimizing power consumption. The primary design approach employed in our design involves the utilization of unary operators and specialized transistor configurations to reduce the number of transistors and shorten the critical path. We used the Hewlett simulation program with integrated circuit emphasis (HSPICE) and GNRFET technology with a 32-nm channel length operating at 0.9 V and 300˚ K to evaluate the efficiency of our circuit. We then compared it with similar existing ternary multiplier circuits. The suggested circuit displays favorable delay and power consumption characteristics and ranks as the second most optimal design in terms of energy efficiency. Furthermore, it improves the energy-delay-product by at least 2.80%.

Graphical Abstract

Keywords

References

[1] Anil D. G., Bai Y., Choi Y., (2018), Performance evaluation of ternary computation in SRAM design using graphene nanoribbon field effect transistors," in

2018 IEEE 8th Annual Computing and Communication Workshop and Conference (CCWC), pp. 382-388.

https://doi.org/10.1109/CCWC.2018.8301723[2] Nikbakht E., Dideban D., Moezi N., (2020), A half adder design based on ternary multiplexers in carbon nano-tube field effect transistor (CNFET) technology.

ECS J. Solid State Sci. Technol. 9: 081001.

https://doi.org/10.1149/2162-8777/abb588[3] Nayeri M., Keshavarzian P., Nayeri M., (2019), Approach for MVL design based on armchair graphene nanoribbon field effect transistor and arithmetic circuits design.

Microelectron. J. 92: 104599.

https://doi.org/10.1016/j.mejo.2019.07.017[5] Tabrizchi S., Azimi N., Navi K., (2017), A novel ternary half adder and multiplier based on carbon nanotube field effect transistors.

Frontiers of Inform. Technol. Electronic Eng. 18: 423-433.

https://doi.org/10.1631/FITEE.1500366[7] Pelletier B., Juhel M., Trouiller C., Beucher D., Autran J., Morin P., (2008), Boron out-diffusion mechanism in oxide and nitride CMOS sidewall spacer: Impact of the materials properties.

Mater. Sci. Eng: B. 154: 252-255.

https://doi.org/10.1016/j.mseb.2008.09.025[8] Chen Y.-Y., Sangai A., Rogachev A., Gholipour M., Iannaccone G., Fiori G. (2015), A SPICE-compatible model of MOS-type graphene nano-ribbon field-effect transistors enabling gate-and circuit-level delay and power analysis under process variation.

IEEE Transact. Nanotechnol. 14: 1068-1082.

https://doi.org/10.1109/TNANO.2015.2469647[9] Gholipour M., Chen Y.-Y., Sangai A., Masoumi N., Chen D., (2015), Analytical SPICE-compatible model of Schottky-barrier-type GNRFETs with performance analysis.

IEEE Transact. Very Large Scale Integration (VLSI) Systems. 24: 650-663.

https://doi.org/10.1109/TVLSI.2015.2406734[10] Radsar T., Khalesi H., Ghods V., (2020), Improving the performance of graphene nanoribbon field-effect transistors by using lanthanum aluminate as the gate dielectric.

J. Comp. Electron. 19: 1507-1515 .

https://doi.org/10.1007/s10825-020-01557-8[12] Zarandi A. D., Reshadinezhad M. R., Rubio A., (2020), A systematic method to design efficient ternary high performance CNTFET-based logic cells.

IEEE Access. 8: 58585-58593. .

https://doi.org/10.1007/s10825-020-01557-8[13] Jaber R. A., Kassem A., El-Hajj A. M., El-Nimri L. A., Haidar A. M., (2019), High-performance and energy-efficient CNFET-based designs for ternary logic circuits.

IEEE Access. 7: 93871-93886. .

https://doi.org/10.1007/s10825-020-01557-8[15] Abbasian E., Orouji M., Taghipour Anvari S., Asadi A., Mahmoodi E., (2023), An ultra low power and energy‐efficient ternary Half‐Adder based on unary operators and two ternary 3 : 1 multiplexers in 32-nm GNRFET technology. Int. J. Circuit Theory Applicat. 51: 4969-4983.

[16] Abbasian E., Aminzadeh A., Taghipour Anvari S., (2023), GNRFET-and CNTFET-based designs of highly efficient 22 T unbalanced single-trit ternary multiplier cell.

Arab. J. Sci. Eng. 1-16. .

https://doi.org/10.1007/s10825-020-01557-8[17] Abbasian E., Nayeri M., (2023), A high-speed low-energy one-trit ternary multiplier circuit design in CNTFET technology.

ECS J. Solid State Sci. Technol. 12: 89-95.

https://doi.org/10.1007/s10825-020-01557-8[18] Rohani Z., Emrani Zarandi A. A., (2023), A power efficient 32 nm ternary multiplier using Graphene nanoribbon field-effect transistor technology.

ECS J. Solid State Sci. Technol. 12:47-52. .

https://doi.org/10.1007/s10825-020-01557-8[19] Jaber R. A., Aljaam J. M., Owaydat B. N., Al-Maadeed S. A., Kassem A., A. Haidar M., (2021), Ultra-low energy CNFET-based ternary combinational circuits designs.

IEEE Access. 9: 115951-115961. .

https://doi.org/10.1007/s10825-020-01557-8[21] Srinivasu B., Sridharan K., (2016), Low-complexity multiternary digit multiplier design in CNTFET technology.

IEEE Transact. Circuits and Systems II: Express Briefs. 63: 753-757. .

https://doi.org/10.1007/s10825-020-01557-8[25] Abbasian E., Mirzaei T., (2022), A stable low leakage power SRAM with built-In read/write-assist scheme using GNRFETs for IoT applications.

ECS J. Solid State Sci. Technol. 11: 791-796.

https://doi.org/10.1007/s10825-020-01557-8[27] Sadjadi M. A, Sadeghi B., Zare K., (2007), Natural bond orbital (NBO) population analysis of cyclic thionylphosphazenes, [NSOX (NPCl2)2]; X=F(1), X = Cl(2).

J. Mol. Struc: Theochem. 817: 27-33.

https://doi.org/10.1016/j.theochem.2007.04.015[28] Mani E., Abbasian E., Gunasegeran M., Sofimowloodi S., (2022), Design of high stability, low power and high speed 12 T SRAM cell in 32-nm CNTFET technology.

AEU-Int. J. Electron. Communic. 154: 154308-154313.

https://doi.org/10.1007/s10825-020-01557-8