Novel design methodologies of digital circuits have been caught in the spotlight of attention as a result of the dramatic increase in available data and the requirement for data processing among which Full adder cells are significant elements in arithmetic circuits design. The use of approximate computing and Multi Value Logic (MVL) can improve computational […]

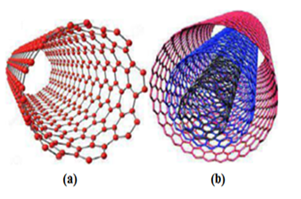

Full adder cells are the major fundamental elements of larger arithmetic circuits, which are mostly located along the critical path of circuits. Therefore, the design of low-power and high-speed full adder cells is critical. In this paper, there are two new inexact full adder cells proposed based on Carbon Nanotube Field Effect Transistor (CNFET) technology. Using the HSPICE simulator […]