A Low Complexity Multi-Valued Logic Successor and Predecessor in Nanoelectronics

Authors

Abstract

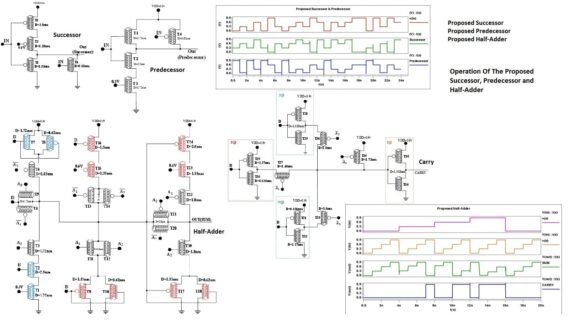

Extremely efficient successor and predecessor circuits are suggested in this article using 4 CNTFETs. They have much fewer interconnections and complexity compared to the best previous circuits. The proposed circuits are designed by combining digital and analog techniques for the first time. They can be expanded for all MVLs like ternary, quaternary, pentaternary, and so on. The proposed designs for quaternary logic reduce the transistor count from 25 to 4 in comparison with the best previous works. Interestingly, in MVLs with more level logic, this difference will increase dramatically. This advantage leads to low complexity and costs. The accurate operation and great performance of introduced circuits are illustrated and their superiority is proved. Additionally, a quaternary half-adder is founded on the presented successor and predecessor. The simulation results, which are acquired by comprehensive simulations utilizing Synopsys HSPICE and the 32 nm plenary CNTFET model of Stanford, show that the proposed successor and predecessor circuits with only four transistors work accurately. According to these outcomes, in the proposed half-adder, not only was the transistor count reduced by 32%, but also it had 40% better PDP and 42.05% better EDP in comparison with the best previous work. Also, it is more stable against process variation and robust in a wide range of temperature variations.

Graphical Abstract

Keywords

References

[1] M. Rezaei Khezeli, M.H Moaiyeri, and A. Jalali , “Active shielding of MWCNT bundle interconnects: an efficient approach to cancellation of crosstalk- induced functional failures in ternary logic,” IEEE Trans Electromagn Compat, 61(1), pp. 100-110, 2019.

[2] M. Rezaei Khezeli, M.H Moaiyeri, and A. Jalali, “Comparative analysis of simultaneous switching noise effects in MWCNT bundle and Cu power interconnects in CNTFET-based ternary circuits,” IEEE Trans Very Large Scale, 27, pp. 37-46, Sep. 2018.

[3] M.H Moaiyeri, Z. Hajmohammadi, M. Rezaei Khezeli, and A. Jalali, “Effective reduction in crosstalk effects in quaternary integrated circuits using mixed carbon nanotube bundle interconnects,” ECS J Solid State Sci Technol, 7(5), pp. 69-76, 2018.

[4] M.H Moaiyeri, Z. Mehdizadeh Taheri, M. Rezaei Khezeli, and A. Jalali, “Efficient passive shielding of MWCNT interconnects to reduce crosstalk effects in multiple valued logic circuits,” IEEE Trans Electromagnetic Compatibility, 61(5), pp. 1593 – 1601, Oct. 2019.

[5] R. Kumar, S. Bala, and A. Kumar, “Study and Analysis of Advanced 3D Multi-Gate Junctionless Transistors,” Springer. J. Silicon, pp. 1053–1067, Dec. 2020.

[6] S.A Ebrahimi, M.R Reshadinezhad, A. Bohlooli, and M. Shahsavari, “Efficient CNTFET based design of quaternary logic gates and arithmetic circuits,” Microelectronics J, 53, pp. 156-166, 2016.

[7] S. Bala, and M. Khosla, “Electrostatically doped tunnel CNTFET model for low-power VLSI circuit design,” Springer. J. Computational Electronics, pp. 1528–1535, Sep. 2018.

[8] Y. Pendashteh, and S.A Hosseini, “Novel Low-Complexity and Energy-Efficient Fuzzy Min and Max Circuits in Nanoelectronics,” Int. J. Electron. Commun. (AEÜ), 138, Jun. 2021.

[9] M.H Moaiyeri, M. Shamohammadi, F. Sharifi, and K. Navi, “High-performance ternary logic gates for Nano-electronics,” Int. J. High Performance, Syst. Architecture, 5(4), pp. 209-215, Nov. 2015.

[10] S. Etezadi, and S.A Hosseini, “Novel Ternary Logic Gates Design in Nano-electronics,” Theoretical and Applied Elect. Engineering, 17 (3), pp. 294-305, Sep. 2019.

[11] F. Sharifi, M.H Moaiyeri, K. Navi, and N. Bagherzadeh, “Robust and energy-efficient carbon nanotube FET- based MVL gates: A novel design approach,” Elsevier Microelec. J. 46(12), Part. A, pp. 1333-1342, Dec. 2015.

[12] K. Rahbari, and S.A Hosseini, “Novel ternary D-Flip-Flap-Flop and counter based on successor and predecessor in nanotechnology,” Int. J. Electron. Commun. (AEÜ)., 109, pp. 107–120, Jul. 2019.

[13] E. Roosta, and S.A Hosseini, “A Novel Multiplexer- Based Quaternary Full Adder in Nano-electronics,” Springer. J. Circuits, Syst. Signal Process., 38(9), pp. 4056–4078, Sep. 2019.

[14] F. Sharifi, M.H Moaiyeri, K. Navi, and N. Bagherzadeh, “Quaternary full adder cells based on Carbon nanotube FETs,” Springer. J. Comput. Electron. 14, pp. 762–772, 2015.

[15] A. Daraei, S.A Hosseini, “Alternative Design Techniques of Quaternary Latch, Flip-Flops and Counters in Nanoelectronics,” International Journal of Electronics, pp. 669-698, Aug. 2021.

[16] S.A Hosseini, S. Etezadi, “ A Novel Low-Complexity and Energy-Efficient Ternary Full Adder in Nanoelectronics,” Circuits, Systems, and Signal Processing 40 (3), pp. 1314-1332, 2021.

[17] M. Shahangiyan, S.A Hosseini, and R. Faghih Mirzaee, “A Universal Method for Designing Multi-Digit Ternary-to-Binary Converter Using CNTFET,” Circuits.Syst. Computers. J, 29(12), 2020.

[18] M. Ghelichkhan, S.A Hosseini, and S.H Pishgar Komleh, “Multi-digit Binary-to-Quaternary and Quaternary-to- Binary Converters and Their Applications in Nano-electronics,” Springer. J. Circuits, Syst. Signal Process., 39, pp. 1920–1942, Aug. 2019.

[19] S.A Hosseini, E. Roosta , “A novel low complexity and energy-efficient method to implement quaternary logic function in nanoelectronics,” Microelectronics Journal 102, Aug. 2020.

[20] Stanford University Nano-electronics Group. Stanford University CNTFET Model. http://nano.stanford.edu/model.php?id=23.

[21] A. Singh, M. Khosla, and B.Raj, “Design and analysis of electrostatic doped Schottky barrier CNTFET based low power SRAM,” Int J Electron Commun (AEÜ)., 80, pp. 67-72, 2017.

[22] S.J Tans, A.R.M Verschueren, C. Dekker C, “Room-temperature transistor based on a single carbon nanotube,” Nature, 393, pp. 49-52, 1998.

[23] J. Deng, H. Wong, “A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part I: Model of the intrinsic channel region,” IEEE Trans Electron Dev, 54(12), pp. 3186-3194, 2007.

[24] s. Lin, Y.B Kim, and F. Lombardi, “CNTFET-based design of ternary logic gates and arithmetic circuits,” IEEE Trans. Nanotechnol., 10(2), pp. 217–225, Mar. 2011.

[25] M. Honaryar, S.A Hosseini, S.H Pishgar Komleh, “A Novel model of binary and ternary Schmitt triggers based on multi-threshold voltage in nanoelectronics,” Int. J. Electron. Commun. (AEÜ)., 137, May. 2021.

[26] D. Miller, M. Thornton, “Multiple Valued Logic: Concepts and Representations,” Synthesis Lectures on Digital Circuits and systems, Morgan& Claypool publishers, 2007.

[27] B. Razavi, “Design of Analog CMOS integrated circuits,” Boston, McGraw-Hill, 2001.

[28] Z. Davari Shalamzari, A. Dabbaghi Zarandi, M.R Reshadinezhad, “Newly multiplexer-based quaternary half-adder and multiplier using CNTFETs,” Int. J. Electron. Commun. (AEÜ), 117, 2020.

[29] M.H Moaiyeri, K. Navi, O. Hashemipour, ”Design and evaluation of CNTFET- based quaternary circuits,” Circuits, Syst. , SignalProcess. 31(5), pp. 1631- 1652, 2012.

[30] S.A Hosseini, S. Etezadi, “Low storage power and high noise margin ternary memory cells in nanoelectronics,” IET Circuits, Devices & Systems 14 (7), pp. 929-94, Oct. 2020.

[31] S.A Hosseini, E. Roosta, “A Novel Technique to Produce Logic ‘1’in Multi-threshold Ternary Circuits Design,” Circuits, Systems, and Signal Processing 40 (3), pp. 1152-1165, 2021.