To appear in: Majlesi Journal of Electrical Engineering (MJEE)

This PDF file is not the final version of the record. This version will undergo further copyediting, typesetting, and production review before being published in its definitive form. We are sharing this version to provide early access to the article. Please be aware that errors that could impact the content may be identified during the production process, and all legal disclaimers applicable to the journal remain valid.

| Received: 12 March 2025         | Revised: 2 July 2025 |

|---------------------------------|----------------------|

| Accepted: 9 July 2025           |                      |

| DOI: 10.57647/j.mjee.2025.17076 |                      |

#### **Original Research**

### A New ZVS Multi-input Converter with Modular Auxiliary Circuit and Low Voltage Stress for Renewable Energy Applications

Authors: Mehdi Khodadadian Zaghmari 1 , Majid Delshad 1, Mohammadali Abbasian 1

🔍 Mohammad Rouhollah Yazdani 🗓

1- Department of Electrical Engineering, Isfahan (Khorasgan) Branch, Islamic Azad University, Isfahan, Iran.

\*Corresponding author: delshad@khuisf.ac.ir

© Author(s) 2025

#### **Abstract**

Renewable energy sources like wind and solar power experience output voltage fluctuations due to changing weather conditions. To maintain a stable power supply, integrating multiple input sources is essential. A Multi-Input Converter (MIC) provides a more efficient solution by reducing the need for numerous passive components, which in turn minimizes cost, size, and weight compared to separate converters. This study introduces a dual-input boost converter with zero voltage switching (ZVS), utilizing a single auxiliary circuit to enable soft switching for all semiconductor elements. This design not only improves efficiency but also retains the advantages of multi-input converters. Additionally, a voltage multiplier is incorporated to enhance the voltage conversion ratio, achieving higher voltage gains. The theoretical analysis of the proposed converter is validated through experimental results, with efficiency measurements demonstrating a 3% improvement over conventional hard-switching designs.

KEYWORDS: DC-DC converter; Coupled inductor; High-gain; Soft-switching.

| NOMENCLA | TURE                    |     |                         |

|----------|-------------------------|-----|-------------------------|

| ZCT      | Zero current Transition | ZVT | Zero Voltage Transition |

| MIC      | Multi-Input Converter   | VR  | voltage regulation      |

| PFC             | Power Factor Correction      | ZCS | zero current switching |

|-----------------|------------------------------|-----|------------------------|

| EMI             | electromagnetic interference | ZVS | zero voltage switching |

| I <sub>lm</sub> | Magnetizing current          | n   | Turn ratio             |

| l <sub>ik</sub> | Leakage inductance current   | m   | Tertiary turn ratio    |

| V <sub>DS</sub> | Drain source voltage         | D   | Duty cycle             |

| ω               | Angular frequency            | Vcs | Snubber voltage        |

#### 1. INTRODUCTION

In boost converters, the rapid switching of power devices leads to considerable switching losses. To achieve high voltage gain, various topologies and techniques have been developed in traditional boost converter designs [1]–[3]. These converters offer multiple benefits, including enhanced transient response, improved thermal management, reduced current ripple, and increased reliability [4], [5]. In multi-phase buck converters, increasing the number of switching stages within a single phase effectively raises the input current's frequency, thereby reducing overall current ripple [5], [6]. Additionally, multi-phase converters improve efficiency by distributing the load current across several phases, which minimizes voltage drops and conduction losses in semiconductor devices. Higher switching frequencies can further enhance the transient response and power density of DC-DC converters [4]. However, operating at higher switching frequencies can also result in reduced overall efficiency and increased switching losses [9], [10].

One of the main challenges in high-frequency converters is electromagnetic interference (EMI). both active [7], [8] and passive [9], [10] switching techniques have been proposed. Among active methods, Zero Voltage Transition (ZVT) is widely regarded as a simple yet effective solution, especially in converters utilizing MOSFETs. ZVT achieves reduced switching losses and lower EMI by enabling or disabling the MOSFET at zero voltage [11]-[13]. Furthermore, optimizing ZVT-based converters by minimizing the number of components in the ZVT cell and employing a single ZVT cell across multi-stage converter structures can significantly reduce both the overall cost and physical size of the converter. Recent studies have explored a range of converter topologies, including those employing boost configuration with particular emphasis on ZVT implementations. Despite their advantages, many of the proposed topologies suffer from certain drawbacks, such as increased component count, added complexity, and reduced efficiency under specific operating conditions.

- 1. The high complexity and large number of components significantly increase both the overall cost and physical size of the circuit.

- 2. The need for diode replacement along with the associated costs and electromagnetic interference (EMI) issues—can be mitigated through timely maintenance or the use of alternative solutions.

- 3. The inclusion of one or more switches in the gate driver control circuit further contributes to system complexity.

In [14], a Zero Voltage Transition (ZVT) soft-switching boost converter is introduced, incorporating an auxiliary circuit with two auxiliary switches configured within a two-phase amplifier. However, this design results in increased voltage stress on the main switch. In contrast, [15] proposes a soft-switching poly-phase boost converter that integrates a resonant choke into its ZVT implementation, but it requires DC auxiliary switches and floating gate control for each phase, adding to design complexity. Recent works [16]–[23] have proposed various methods to reduce the number of active components in converter circuits. For instance, the converters presented in [16]-[18] achieve smooth operation of the main switch by using an auxiliary switch; however, these configurations still rely on additional semiconductor elements. Notably, [16] requires the auxiliary switch to operate four times per switching cycle, thereby doubling the number of switching states. This extended operation increases conduction time and leads to higher power dissipation [17]. Alternatively, [19] investigates a boost converter design that mitigates additional current and voltage stress on the main switch. Nevertheless, its twophase structure requires additional components, including two inductors and four diodes. In [20], a ZVT boost converter is reviewed that employs an auxiliary switch and features a relatively simple switching mechanism. Despite this simplicity, it necessitates a high-voltage current converter to maintain load supply during the extended activation of the auxiliary circuit, resulting in increased conduction losses. Efforts in [21]-[23] aim to simplify the converter topology by minimizing component count. However, the converter described in [21] is limited by switching frequency constraints, inadequate filtering performance, and elevated stress on the converter switch. Similarly, the inverter presented in [22] demands a secondary switch for sliding gate control and requires a dedicated magnetic core for the secondary winding. In the ZVT design proposed in [23], synchronous rectifier switches are repurposed as auxiliary switches, eliminating the need for additional switching elements. While effective, this method is only applicable to transformer-based systems that already include synchronous rectifiers.

It also significantly reduces voltage and current stresses on switch. A simpler ZVT converter design is presented in [24], featuring a streamlined circuit structure; however, it still employs multiple auxiliary components and imposes both current and voltage stress on the auxiliary switch. Reference [25] highlights the inclusion of multiple auxiliary elements in a two-phase transformer design, while [21] describes a frequency-controlled approach. A buck converter with comparable characteristics is also noted in [26], which, although more compact, encounters similar limitations as those reported in [21] and [25]. This paper presents a comprehensive review of a family of interconnected ZVT converters and their various configurations. The proposed design utilizes a single auxiliary circuit, enabling all semiconductor devices to operate in a simple switching mode with only one switch and without the need for chokes, thereby improving efficiency during load variations. In this configuration, the converters employ Zero-Voltage Switching (ZVS) for the main switches and Zero-Current Switching (ZCS) for the auxiliary switches. Moreover, the leakage inductance of the coupled windings can control the output current, reduce stress on complementary diodes, and reduce issues related to reverse recovery. The converter uses transformer cores with couple windings that function as voltage sources, effectively reducing the current in the secondary circuit to zero once the ZVS switch is activated. The integrated ZVT cell absorbs the leakage inductance of the coupled coils and utilizes the parasitic MOSFET capacitors as suppression capacitors. This integration eliminates the need for additional resonance inductance, significantly lowering the cost, weight, and size of the auxiliary circuit. The proposed ZVT converters were theoretically validated through a step-up design process, and a 300 W boost converter prototype operating at 100 kHz was built to confirm the experimental results. Furthermore, additional variants of the converter family have been developed based on the ZVT concept, with new versions. While a basic ZVT cell was introduced in [27], its application was initially confined to single-phase converters and did not extend to other two-input DC-DC converter types. In this study, the cell is employed to develop a full series of low-cost, compact, and soft ZVT AC converters, all sharing a common sub-circuit.

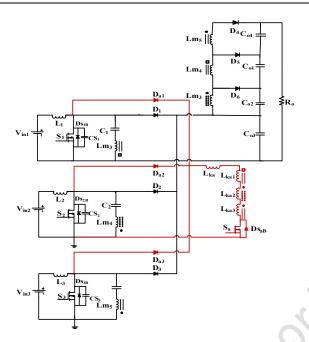

# 2. THE PROPOSED ZVT DUAL-INPUT HIGH STEP-UP CONVERTER INTEGRATES TWO INPUTS

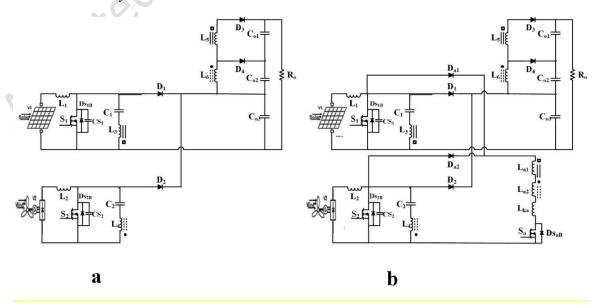

Figure 1(a) illustrates Conventional designs for dual-input step-up converters Figure 1(b) illustrates Proposed ZVT dual input step-up converter, along with the core structure of the ZVT cell. The primary inductors, L3 and 4, are connected to the auxiliary input terminals La1 and La2, which in turn are linked to inductors L5 and L6. Switches S1 and S2 are the main switches, while D1 and D2 function as input diodes. Vin1, Vin2, and Vout denote the input and output voltages, respectively. CS1 and CS2 are the snubber capacitors for switches S1 and S2. Co is the output filter capacitor, and Ro represents the load. The equivalent circuit of the converter is also depicted in Figure 1(b), where N1, N2 and N3 correspond to the number of turns in each of the three windings. Lm3, Lm4 are magnetic inductances, with LKa representing both the leakage inductance on one side of the transformer and the magnetically induced inductance from primary to secondary. Additional components include a switch and diodes Da1 and Da2. All winding ratios are assumed to be equal, and the Na/N ratio is defined as proportional to n. A minor transformation occurs in the converter when the duty cycle (D) is less than 50%. For D > 50%, the operational characteristics are detailed below. Each primary circuit operates across fourteen distinct switching modes. However, due to the symmetry in the dual-input topology, only seven modes related to the operation of main switch S1 are analyzed in detail.

FIGURE 1. (a) Conventional designs for dual-input step-up converters. (b) Proposed ZVT dual input step-up converter.

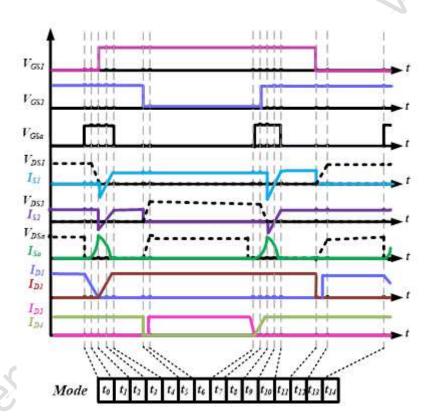

Figures 2 and 3 provide the corresponding waveform diagrams and equivalent circuits for each mode. Prior to time  $t_0$ , switch  $S_2$  and diode  $D_1$  are assumed to be turned off, while all other semiconductor devices are in the on-state. At this moment,  $C_{S1}$  is charged to the output voltage  $V_{out}$ .

Mode 1 [ $t_0$ – $t_1$ ] (Figure 3(a)): To charge  $C_{S1}$  and enable Zero-Voltage Switching (ZVS) for switch  $S_1$ , the auxiliary circuit must be activated prior to applying the gate signal to  $S_1$ . At time  $t_0$ , auxiliary switch  $S_a$  is turned on. Due to the presence of series leakage inductance  $L_{k1}$ , both diode  $D_{a1}$  and switch  $S_a$  conduct under Zero-Current Switching (ZCS) conditions. As a result of the positive voltage across  $L_{Ka}$ , the current  $I_{Lka}$  begins to rise, while the current through diode  $D_1$  ( $I_{D1}$ ) decreases accordingly. At time  $t_1$ , the diode current  $I_{D1}$  reaches zero, turning  $D_1$  off under ZCS conditions and thereby ending this switching mode. During this interval, the circuit behavior can be described by the following equations:

$$ILka(t) = \frac{Vout [1 - n(1 - 2D)](t - t0)}{I.ka}$$

(1)

FIGURE 2. Theoretical waveforms.

$$I_{D1}(t) = I_{L1}-(n+1) I_{lka}(t)$$

(2)

where  $I_{L1}$  represents the current through  $L_1$ , which equals half of the midpoint input current  $(I_{in1}/2)$ , accounting for the distribution between the two components.

**Mode 2** [ $t_1$ – $t_2$ ] (Figure 3(b)): At time  $t_1$ , diode  $D_1$  turns off, initiating a resonant transition between capacitor  $C_{S1}$  and inductor  $L_{Ka}$ . By the end of this mode, the energy initially stored in  $C_{S1}$  is fully transferred to  $L_{Ka}$ , resulting in the voltage across  $C_{S1}$  ( $V_{CS1}$ ) dropping to zero. At this moment, switches  $S_1$  and  $S_2$  are turned on under ZVS conditions. The corresponding resonance behavior can be described by the following equation:

$$I_{Lka}(t) = A + Bsin(\omega(t - t_1))$$

(3)

$$V_{Cs1}(t) = \left[L_{Ka} \frac{dI_{lka}}{dt} + 2nV\right] \frac{1}{n+1}$$

(4)

Where

$$\omega = \frac{n+1}{\sqrt{L_{ka} C_{s1}}} \tag{5}$$

$$A = \frac{I_{lm}}{n+1} \tag{6}$$

$$\frac{P_{\text{Mail}}[1-\pi(1-2D)]}{B_{\text{Mass}}} \qquad (7)$$

FIGURE 3. Equivalent circuit models of each mode.

**Mode 3** [ $t_2$ – $t_3$ ] (Figure 3(c)): At time  $t_2$ , the anti-parallel diodes of  $S_1$  and  $S_2$  are turned on. During this mode, the voltage decreases due to a voltage source associated with  $I_{Lka}$ , with the expression -( $VL_{a1} + VL_{a2}$ ) = -2 $nV_{in}$ , which results from the secondary side reflection of  $L_1$  and  $L_2$ . The anti-parallel diodes,  $T_3$ ,  $S_1$ , and  $S_2$ , turn off under Zero Current Switching (ZCS), marking the end of this mode. During this interval, the gate signal for  $S_1$  can be applied,

enabling the switch to turn on under Zero Voltage Switching (ZVS) conditions, while the current through D3 increases under ZCS conditions. The following equation applies to this mode:

$$I_{sa}(t) = I_{ka}(t) = I_{ka}(t_2) - \frac{2n(1-D) V_{out}}{L_{ka}} (t - t_2)$$

(8)

where  $I_{Lka}(t_2)$  can be determined from the previous equation (3) by substituting  $t_2$  for t.

Mode 4 [t<sub>3</sub>-t<sub>4</sub>] (Figure 3(d)): In this mode,  $I_{Lka}$  decreases linearly at a constant rate until it becomes zero at t<sub>4</sub>, which leads to  $S_a$  turning off under ZCS conditions.

Mode 5 [t<sub>4</sub>-t<sub>5</sub>] (Figure 3(e)): In this mode, both main switches are activated, while the auxiliary circuit is turned off. L<sub>1</sub> and L<sub>2</sub> are linearly charged by the input voltage source V<sub>in</sub>, while the output capacitor supply the load.

**Mode 6** [ $t_5$ – $t_6$ ] (Figure 3(f)): At the start of this mode, the ZVS condition of  $S_2$  is interrupted by the capacitor  $C_{S2}$ . During this transition, the current in  $L_2$  charges  $C_{S2}$  almost linearly. At  $t_6$ , the drain-source voltage of  $S_2$  ( $V_{DS2} = V_{CS2}$ ) increases to  $V_{out}$ , causing  $D_2$  to turn on. The following equation can be written for this period:

$$V_{Ds2} = V_{CS2} = \frac{I_{L2}}{C_{S2}} (t - t_4)$$

(9)

Here  $I_{L2}$  is the current  $L_2$ .

Mode 7 [ $t_6$ – $t_7$ ] (Figure 3(g)): During this mode, the stored energy is transferred to the gate of  $L_2$ , while  $L_1$  continues to be linearly charged by  $V_{in1}$ . At  $t_7$ , the second half of the switching cycle starts, and the auxiliary switch is turned on once more to sustain the ZVS condition for  $S_2$  as it turns off.

#### 3. ANALYSIS OF THE CONVERTER

To achieve Zero Voltage Switching (ZVS) for the main switches, diode  $D_1$  must turn off at time  $t_1$ , initiating a resonant loop with inductor  $L_{Ka}$ .  $L_{Ka}$  is part of the auxiliary circuit, which also includes capacitor  $C_{S1}$  and the output voltage across the three inductors. This resonant loop enables the discharge of  $C_{S1}$ . Consequently, the inductance in the auxiliary circuit must be lower than the equivalent impedance determined by the output voltage, establishing a design criterion valid for any n > 0. According to Equation (4),  $C_{S1}$  can be fully discharged in Mode 2, provided certain conditions are met. The minimum required time interval to turn off the switch and trigger diode conduction is denoted as  $T_{ZVT}$ , which is the combined duration of Modes 1 and 2. Specifically,  $T_{ZVT}$  represents the minimum delay before applying the main gate signal to the switch. ZVS occurs when the main switch turns off with zero voltage across its, minimizing switching losses. Zero Current Switching (ZCS), on the other hand, occurs when the auxiliary switch turns on with zero current through it, also reducing switching losses. To maintain ZCS, it is essential to remove the control signal from the auxiliary gate once the auxiliary current ( $I_{Sa}$ ) drops to zero. The time during which the auxiliary switch remains off is critical for sustaining ZVS during the transition of the main switch between its on and off states. Proper synchronization is important to ensure efficient operation of both switches, minimizing energy losses and maintaining soft-switching performance.

#### 3.1. VOLTAGE GAIN

The voltage conversion ratio, which relates the output voltage to each input source voltage, can be formulated as:

$$V_{co3} = \frac{Vin1}{(1-D1)} OR \frac{Vin2}{(1-D2)}$$

(10)

$$V_{col} = \frac{nD1}{(1-D1)} \tag{11}$$

$$V_{co2} = \frac{mD2Vin2}{(1-D2)}$$

(12)

$$V_0 = V_{co1} + V_{co2} + V_{co3} = \frac{(1 + nD1)Vin1(1 - D2) + mD2Vin2(1 - D1)}{(1 - D1)(1 - D2)} (13)$$

If  $V_{in1}=V_{in2}$  and  $D_1=D_2$  the voltage conversion ratio It can be considered as such:

$$\frac{Vo\_1+(m+n)D}{Vin} \qquad \qquad (14)$$

$$m=n \rightarrow Gain = \frac{Vo}{Vin} = \frac{1+2nD}{1-D}$$

(15)

#### 3.2. VOLTAGE STRESSES ATHWART POWER SWITCHES AND DIODES

The association between the output voltage and the voltage of the individual input sources can be written as Semiconductors are designed to endure the voltage applied to them, which is required. The proposed converter has less voltage across the current switches/diodes, so it works in the same way as a conventional step-up converter. The power converter can be calculated using the following equation:

$$V_{s1} = V_{s2} = V_{D1} = V_{D2} = \frac{V_0}{1 + 2nD}$$

(16)

$$V_{s3} = V_{D3} = \frac{V_0}{1 + 2nD} + V_{Cr,p}$$

(17)

$$V_{s3} = V_{D3} = \frac{V_0}{1 + 2nD} + V_{Cr,p}$$

$$V_{D5} = V_{D4} = \frac{V_0(n+1) - 1}{1 + 2nD}$$

(17)

#### 3.3. DESIGN PROCESS

The design of the converter is presented, and the conversion process is demonstrated using the example of a twophase ZVT converter. In this case, the input voltages are  $Vin_1 = 24 \text{ V}$  and  $Vin_2 = 96 \text{ V}$ , with an output voltage of Vout = 310 V, a total output power of 300 W, and a switching frequency of  $f_{sw} = 100 \text{ kHz}$ . Based on the characteristics of the operating structure, it is assumed that  $L_1 = L_2 = Lin$ ,  $C_{S_1} = C_{S_2} = C_S$ , and that  $S_1$  is identical to  $S_2$ , as well as  $D_1$  being identical to  $D_2$ .

#### 3.4. SELECTION OF PASSIVE ELEMENTS

The magnetic inductors ( $L_{m3}$ ,  $L_{m4}$ ,  $L_{m5}$ ,  $L_{m6}$ ,  $L_{Ka1}$ , and  $L_{Ka2}$ ) and the output capacitor (Co), used as amplifier inductors, are designed similarly to a simple boost converter, as referenced in [28]. As illustrated in Table 2, a 10 μF electrolytic capacitor was used for C<sub>O1</sub>, C<sub>O2</sub>, and C<sub>O3</sub>, with an inductance value of 200 µH for Lin To maintain continuous conduction mode (CCM) operation. According to equations (14) and (15), the voltage across the switch and the output diode is 330 volts. Therefore, the C3M0015065D can be selected as the main switch, and the MUR860 as the diode. The same semiconductor and diode types can be used for ZVT cells, as detailed in the following section.

#### 3.5. AUXILIARY CIRCUIT CONFIGURATION

The auxiliary circuit is primarily designed to enable soft switching for the main switches while ensuring smooth transitions for all other semiconductor devices. Due to simple structure of The auxiliary circuit, only the values for L<sub>Ka</sub>, C<sub>S</sub>, and the turns ratio n need to be determined.

- Capacitors and snubber inductances are selected as 1 nF and 100 µH, respectively, as referenced in [29]. Thus, 100 μH is chosen for the snubber inductance used. This value can be achieved with

- The condition  $I_{Lka}(t_2) = I_{Sa}(max)$  must exceed the combined maximum values of  $I_{L1}(max)$  and I<sub>L2</sub>(max) to ensure that the anti-parallel diodes S<sub>1</sub> and S<sub>2</sub> operate in mode 3 under Zero Voltage Switching (ZVS) conditions.

- Once the snubber capacitor  $L_{Ka}$  is discharged, the auxiliary switch should be turned off as quickly as possible to minimize conduction losses in the auxiliary circuit and impose less limitations on the duty cycle (D). Additionally, it should be turned off before the main switch S<sub>2</sub> is activated. In other words, the duration of mode 3 and 4 ( $t_{2,4} = t_4 - t_2$ ) should be much shorter than  $t_{2,5}$ =  $t_5$  -  $t_2$ , as shown in Figure 2.

$$T_{25(min)} = D_{min} T_{SW} - \frac{T_{SW}}{2}. \tag{19}$$

$$T_{24(max)} \le 0.2 * t_{25(min)}$$

(20)

where:

T<sub>SW</sub> represents the switching time. Therefore, considering Equation (8), the turns ratio n must be greater than 0.26 to satisfy Equation (20).

- 4)The duration of mode 2 should be less than 10% of the total transmission mode duration. From mode (6), C<sub>S</sub> should be less than 8.7 nF.

- 5) The current stress on the auxiliary switch should be less than twice the sum of  $I_{L1}$ (max) and  $I_{L2}$ (max). Therefore, according to Equation (18),  $C_S$  should be less than 1.5 nF.

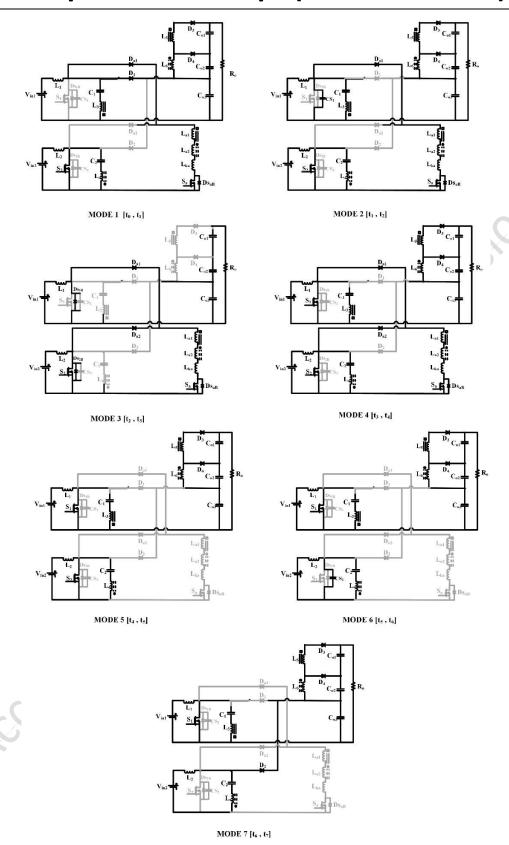

Thus, considering modes 1, 5, and 6, the value of  $C_S$  is chosen to be 1 nF. By selecting these values for  $E_{lka}$ ,  $C_S$ , and n, the situation specified by (10) and (11) will always Be fulfilled. In addition, controller circuit proposed in figure 4. By IC ucc28220 and logic circuit can be made required signal for gates. The parameters have been designed in this way based on practical results.

$$C_{s1} > \frac{Isw tf}{2Vsw} = \frac{0.76*4.5ns}{2*60} = 0.028 \text{ nF} \simeq 1\text{nF}.$$

(21)

$$C_{s2} > \frac{Isw \ tf}{2Vsw} = \frac{0.9*4.5ns}{2*24} = 0.08 \text{ nF} \simeq 1\text{nF}.$$

(22)

$$L_k > \frac{Vsw tr}{Isw} = \frac{150*4.5ns}{0.9} = 0.9uH \approx 10\mu H.$$

(23)

$$I_{c} = c \frac{dv}{dt} = > c = \frac{ic \ dt}{dv} = \frac{Io \ DT}{\Delta Vo} = \frac{Io \ D}{\Delta Vofs} = > C_{o} = \frac{0.9*6.5us}{0.03*100} = 2.92 \mu F , \frac{1}{Co} = \frac{1}{Co1} + \frac{1}{Co} + \frac{1}{Co3} , C_{o1} = C_{o2} = C_{o3} = 8.7 \mu F \approx 10 \mu F.$$

$$(24)$$

$$V_{L} = L \frac{di}{dt} > L = V_{L} \frac{dt}{di} > L_{ml} = \frac{vc_{1} D}{\Delta i f} = \frac{24*7.5 us}{0.01*100} = 180 \mu H \approx 200 \mu H, L_{m2} = \frac{vc_{2} D}{\Delta i f} = \frac{60*6.5 us}{0.02*100} = 195 \mu H \approx 200 \mu H. \quad (25)$$

$$L_{1} = \frac{Vin1 D}{\Delta i f} = \frac{24*7.5us}{0.02*100} = 90 \mu H \approx 100 \mu H, L_{2} = \frac{Vin2 D}{\Delta i f} = \frac{60*6.5u}{0.04*100} = 97.5 \mu H \approx 100 \mu H.$$

(26)

FIGURE 4. (a) Structural diagram of the controller. (b) Generated pulses.

#### 4. POWER LOSSES

This section provides a detailed description of the influence of the non-idea components of the proposed converter on overall losses. Conduction losses in the MOSFET and diode, as well as the conduction losses of the coupled inductors and capacitors, are evaluated by considering non-ideal components. The Zero Voltage Switching (ZVS) condition ensures that no activation drop occurs for the main switch. However, capacitive turn on losses of the auxiliary switch are taken into account. the core losses , which are considered negligible, can be minimized. The conduction losses of the switches are determined based on RMS current, while discharge losses are calculated based on The drain-source on resistance. The conduction loss of a MOSFET can be estimated as follows:

$$P_{\text{Conduction'sw}} = R_{DS} (I_{RMS'S1}^2 + I_{RMS'S2}^2 + I_{RMS'S3}^2) = 0.015(4.12 + 28.09 + 0.32) = 0.49 \text{W}. \tag{27}$$

Due to the Zero-Voltage Switching (ZVS) condition achieved for the main switch, its capacitive turn-on losses are effectively eliminated. Consequently, only the capacitive turn-on losses associated with the auxiliary switch remain, which can be quantified as follows:

$$P_{\text{cto'sa}} = \frac{1}{2} C_{\text{out's}} V_{\text{Sw}}^{2} f_{\text{S}} = \frac{1}{2} *289 *10^{-12} *98^{2} *100 *10^{3} = 0.139 \text{W}. \tag{28}$$

The conduction losses associated with all diodes are determined by their respective forward voltage drops and the average current flowing through each device. These parameters can be derived as follows:

$$V_{f}(I_{avg'D1} + I_{avg'D2} + I_{avg'D3} + I_{avg'D4}) = 1.5(0.9 + 0.94 + 0.82 + 0.8) = 5.19 W.$$

(29)

$$P_{\text{Conduction'D}} = V_f I_{\text{avgDa1}} + V_f I_{\text{avgDa2}} = 1.5(0.01 + 0.036) = 0.069 \text{ W}.$$

(30)

The conduction losses in the inductors are also taken into account due to the presence of their inherent parasitic resistances. These losses are evaluated using the following expressions:

$$P_{\text{Canacitors}} = R_{\text{CI}} I_{\text{RMS}'\text{CI}}^2 + R_{\text{C2}} I_{\text{RMS}'\text{C2}}^2 + R_{\text{Co}} I_{\text{RMS}'\text{Co}}^2 = 0.2 * (0.65)^2 + 0.2 * (0.99)^2 + 2.3 * (0.37)^2 = 0.65 \text{W}. \tag{31}$$

The power losses associated with the capacitors are also taken into account, as they are a function of the equivalent series resistance (ESR) and the current flowing through them. These losses are computed as follows:

$$P_{winding} = R_{L1}I_{RMS'L1}^2 + R_{L2}I_{RMS'L2}^2 + R_{Lm3}I_{RMS'Lm3}^2 + R_{Lm4}I_{RMS'Lm4}^2 + R_{Lm5}I_{RMS'Lm5}^2 + R_{Lm6}I_{RMS'Lm6}^2 + R_{Lka}I_{RMS'Lka}^2 + R_{Lm6}I_{RMS'Lm6}^2 + R_{Lm6}I_{RMS'Lm6}^2 + R_{Lka}I_{RMS'Lka}^2 + R_{Lm6}I_{RMS'Lm6}^2 + R_{Lm6}I_{RMS'Lm6}^2 + R_{Lka}I_{RMS'Lka}^2 + R_{Lm6}I_{RMS'Lm6}^2 + R_{Lm6}I_{$$

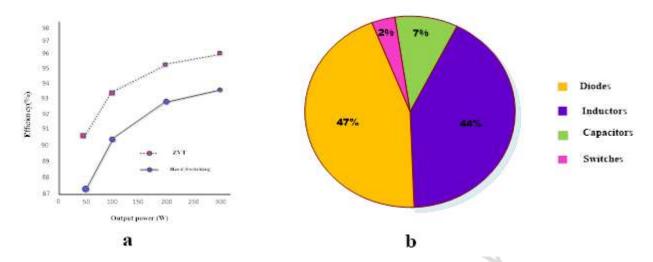

FIGURE 5. (a)Efficiency of the recommended converter. (b)The losses distribution of the recommended converter.

#### 5. EXPERIMENTAL RESULTS

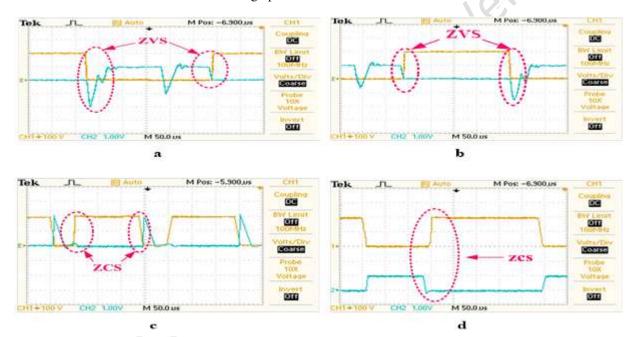

The 300W prototype of the hypothetical converter described in the previous section was created for feasibility testing. All switches and diodes are model numbers C3M0015065D and MUR860. In this section, we present the experimental results for the proposed dual-input converter. Figure 6 shows a photograph of the recommended converter. In Figures 7(a) and (b), it can be observed that the main switches are activated in the Zero Voltage Switching (ZVS) state and disabled in the Zero Voltage (ZV) state. As shown in Figure 7(c), the auxiliary switch is turned off in the Zero Current (ZC) state. The diode in the main circuit is displayed in the zero-voltage state in Figure 7(d). The simulations and theoretical analysis were verified through experiments. However, the current waveforms exhibit some amount of ringing, indicating a discrepancy between the simulations, theoretical analysis, and experimental results. This discrepancy is attributed to the resonance between parasitic capacitors and inductors. Specifically, the resonant inductor and the auxiliary output capacitor resonate at the same frequency. Using data collected under controlled laboratory conditions, a performance curve was generated. The efficiency of the recommended converter is approximately 3% higher than the efficiency of the hard-switching option, as indicated in the graph. This improvement is achieved by eliminating losses such as line losses. efficiency was obtained under test conditions comprising a switching frequency of 100 kHz, an ambient temperature of 60°C, and a nominal load of 200 W.

TABLE 1. Significant design specifications.

| symbol                                                                         | component             | specification |

|--------------------------------------------------------------------------------|-----------------------|---------------|

| $V_{\text{IN1}}$ , $V_{\text{IN2}}$                                            | Input voltage         | 24V,60V       |

| $V_{\text{OUT}}$                                                               | Output voltage        | 310V          |

| $P_{OUT}$                                                                      | Output power          | 300W          |

| $f_{SW}$                                                                       | Switching frequency   | 100kHz        |

| $S_1,S_2,S_a$                                                                  | switches              | C3M0015065D   |

| D <sub>1</sub> ,D <sub>2</sub> ,D <sub>3</sub> ,D <sub>4</sub> ,D <sub>5</sub> | diodes                | MUR860        |

| C <sub>1</sub> ,C <sub>2</sub>                                                 | Charge-pump capacitor | 20μF          |

| Co <sub>1</sub> ,Co <sub>2</sub> ,Co <sub>3</sub>                              | Output capacitor      | $10\mu F$     |

FIGURE 6. Photograph of the Recommended converter.

FIGURE 7. (a). Waveforms of Voltage and current. Main switch  $S_1$ . (b). Waveforms of Voltage and current. Main switch  $S_2$ . (c). Waveforms of Voltage and current. auxiliary switch (d). Waveforms of Voltage and current. main diode  $D_1$ .

#### 6. PRACTICAL EMI TEST RESULTS

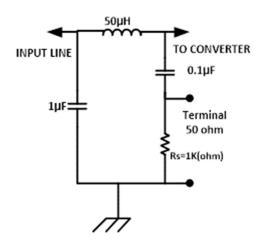

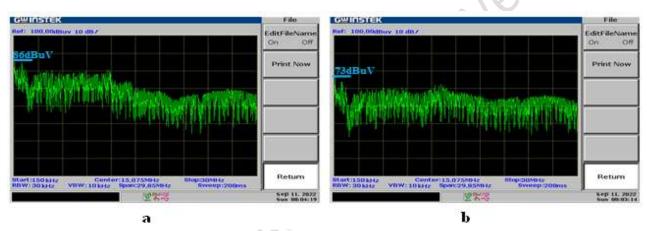

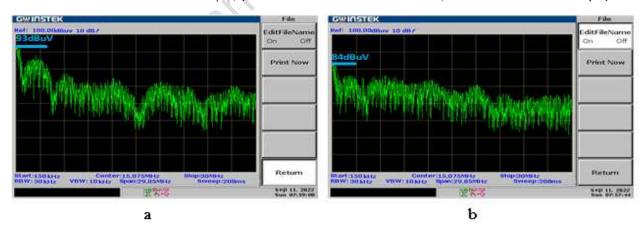

Electromagnetic interference (EMI) measurements were conducted using a CISPR22-compliant LISN and a GWINSTEK GSP-830 spectrum analyzer. The EMI performance of the proposed converter, operating under full load, was compared to that of a conventional hard-switching converter. Both systems used identical components and setups. In this configuration, the spectrum analyzer was connected to the  $R_{\rm S}$ , respectively as shown in Figure 8 and the LISN was placed between the converter's input and the power supply's 24V and 60V outputs [28]. Measurements were taken in peak detection mode to account for the significant influence of common-mode noise on differential-mode interference. Figures 9 and 10 display the EMI characteristics for both converter types. According to the CISPR 22 standard, the conducted EMI frequency range spans from 150 kHz to 30 MHz [29], with EMI levels on the vertical axis ranging from 20 dB $\mu$ V to 100 dB $\mu$ V. Specifically, Figures 9(a) and 10(a) show the EMI of the proposed converter, while Figures 9(b) and 10(b) show the EMI of the hard-switching converter, which recorded peaks of 73 dB $\mu$ V and 84 dB $\mu$ V, respectively. Notably, the proposed converter exhibited an EMI peak of 13 dB $\mu$ V and 84 dB $\mu$ V lower than the peak observed in the hard-switching design.

FIGURE 8. Prototype circuit of CISPR22 LISN [28]

FIGURE9. Full-load EMI Consequences of (a) Hard switching topology for V<sub>input1</sub>. (b) Recommended converter V<sub>input1</sub>, (Horizontal axes: 150 kHz-30 MHz, Vertical axes: 20-100dBμV).

FIGURE 10. Full-load EMI Consequences of (a) Hard switching topology for V<sub>input2</sub>. (b) Recommended converter V<sub>input2</sub>, (Horizontal axes: 150 kHz-30 MHz, Vertical axes: 20-100dBμV).

# 7. COMPARATIVE ANALYSIS OF THE PROPOSED CONVERTER AGAINST ALTERNATIVE DESIGNS

Table 2 provides a comparative analysis between the proposed converter and recently reported topologies in terms of maximum voltage gain, peak voltage stress on switches and diodes, switching technique, efficiency, and the number of components. The converters presented in [30,32],[34,35] and [37-40] lack soft-switching capability

and exhibit lower efficiency compared to the proposed design. Although the topology in [33] achieves a desirable voltage gain and benefits from soft switching, it involves a greater number of components. The converter introduced in [36] features a lower component count with zero-current switching; however, it shows inferior performance in terms of voltage gain and voltage stress, and its main switch is subject to capacitive turn-on losses. The converter in [41] offers an extremely high voltage gain and reduced component count, yet it suffers from high peak voltage stress across both the switch and the diode.

TABLE 2. The comparison of accomplishing the converters and the proposed structure.

| Converter | Voltage gain                                               | Maximum<br>voltage of        | Maximum voltage of          | soft      | oft Efficiency |     | Number of |   |   |     |  |

|-----------|------------------------------------------------------------|------------------------------|-----------------------------|-----------|----------------|-----|-----------|---|---|-----|--|

|           |                                                            | switch                       | diode                       | switching | (%)            | MC* | SW        | D | С | T** |  |

| [30]      | $\frac{3-2D}{(1-D)^2}$                                     | $\frac{V_o}{3-2D}$           | $V_o$                       | Hard      | 91.7           | 3   | 3         | 3 | 3 | 12  |  |

| [31]      | $\frac{5}{1-D}$                                            | $\frac{V_o}{5}$              | $\frac{2V_o}{5}$            | Hard      | 94.24          | 2   | 2         | 5 | 5 | 14  |  |

| [32]      | $\frac{4}{1-D}$                                            | $\frac{V_o}{4}$              | $\frac{V_o}{2}$             | Hard      | 95             | 2   | 2         | 6 | 6 | 16  |  |

| [33]      | $\frac{4}{1-D}$                                            | $\frac{V_o}{4}$              | $\frac{V_o}{2}$             | ZVS       | 95             | 2   | 2         | 8 | 6 | 18  |  |

| [34]      | $\frac{3+D}{1-D}$                                          | $\frac{V_o}{2}$              | $\frac{V_o}{2}$             | Hard      | 94.7           | 2   | 2         | 3 | 3 | 10  |  |

| [35]      | $\frac{2}{1-D}$                                            | $\frac{V_o}{2}$              | $\frac{V_o}{2}$             | Hard      | 90.5           | 2   | 2         | 3 | 4 | 11  |  |

| [36]      | $\frac{n}{1-D}$                                            | $\frac{V_o}{n}$              | $V_o$                       | ZCS       | 94             | 1   | 2         | 4 | 3 | 10  |  |

| [37]      | $\frac{2nD}{1-D}$                                          | $\frac{V_o}{2nD}$            | $\frac{V_o}{2-2D}$          | Hard      | 90.2           | 4   | 2         | 6 | 2 | 14  |  |

| [38]      | $\frac{(2-d_4)(1-d_1)V_2+d_1V_1}{(1-d_1)(1-d_2)(1-d_4)}$   | $\frac{\text{Vin}}{(1-d_1)}$ | $\frac{\text{Vo}}{(2-d_4)}$ | Hard      | 93.5           | 3   | 4         | 4 | 4 | 15  |  |

| [39]      | $\frac{2+n}{1-D}$                                          | $\frac{V_o}{2+n}$            | $\frac{(1+n)V_o}{2+n}$      | Hard      | 94.5           | 1   | 3         | 5 | 3 | 12  |  |

| [40]      | $\frac{V_{in1} + V_{in2}(1 - d_1)}{(1 - d_1)(1 - d_2)}$    | $\frac{(1-d3)V_o}{2}$        | Vo                          | Hard      | 95             | 3   | 3         | 4 | 3 | 13  |  |

| [41]      | $\frac{V_{in2}}{(1-d_1)} + \frac{V_{in1}(1+d_3)}{(1-d_3)}$ | Vo                           | Vo                          | ZVS/ZCS   | 95.5           | 3   | 4         | 3 | 2 | 11  |  |

| proposed  | $\frac{1+2nD}{1-D}$                                        | $\frac{V_o}{1 + 2nD}$        | $\frac{V_o}{1 + 2nD}$       | ZVS       | 96.3           | 2   | 3         | 7 | 5 | 17  |  |

#### 8. EXTRACTION OF AUXILIARY CIRCUIT

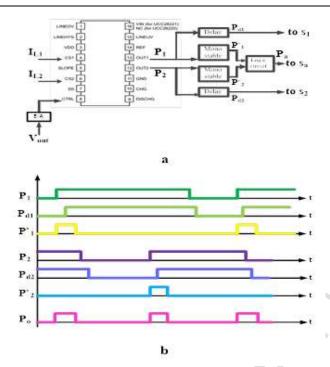

The proposed converter implements a new auxiliary ZVT circuit, designed to use as few components as possible in order to achieve a soft-switching state for the power switch. It is recommended to employ a dual-input boost converter that utilizes zero-voltage transition (ZVT). In addition to the benefits previously discussed for multi-input converters, the efficiency of the recommended converter is enhanced by using a single auxiliary circuit to establish soft-switching conditions for all semiconductor components. A sample of this setup is shown in Figure 11.

FIGURE 11. Extraction high step-up converter with the recommended ZVT auxiliary circuit.

#### 9. CONCLUSIONS

In this study, a novel ZVT converter with dual inputs is proposed. All semiconductor components benefit from the presence of a soft-switching technique. Various operational modes, simulation results, and experimental outcomes are analyzed in conjunction with theoretical predictions. The simulation results demonstrate that the proposed method can improve the efficiency of the converter by approximately 3% at nominal load conditions. The reported efficiency was obtained under test conditions comprising a switching frequency of 100 kHz, an ambient temperature of 60°C, and a nominal load of 200 W.

#### References:

Mirlohi, S. H., Yazdani, M., Amini, M. R. A ZVT Auxiliary Circuit for High Step-Up Multi-Input Converters with Diode-Capacitor Multiplier. Majlesi Journal of Electrical Engineering, 2021; 15(2): 53-64. doi: 10.52547/mjee.15.2.53

Tabasi, M., Bakhshinejad, A. A Novel High Voltage Gain and Low Voltage Stress DC-DC Boost Converter for Photovoltaic Applications. Majlesi Journal of Electrical Engineering, 2018; 12(1): 47-54.

Thirumalaisamy, B., Paul, S., Angappan, N., Subramanian, K. A DC-DC Converter for Electric Vehicle Application. *Majlesi Journal of Electrical Engineering*, 2024; 18(4): 1–10. doi: 10.57647/j.mjee.2024.1804.51.

W. Li, X. He, A family of interleaved DC–DC converters deduced from a basic cell with winding-cross coupled inductors (WCCIs) for high step-up or step-down conversions, IEEE Trans. Power Electron. 23 (2008) 1791–1801. https://doi.org/10.1109/TPEL.2008.925204.

M.Vesali, M. Delshad, E.Adib, M. R. Amini, "A new nonisolated soft switched DC-DC bidirectional converter with high conversion ratio and low voltage stress on the switches," Int. Trans. Electr. Energy Syst., vol. 12, pp. 1–12, 2024. https://doi.org/10.1109/TIE.2010.2089374.

Talgini, H., Delshad, M., Sadeghi, R. A zero voltage transition interleaved DC-DC converter with reduced voltage stress. *Majlesi Journal of Electrical Engineering*, 2025; 19(1): 1–10. doi: 10.57647/j.mjee.2025.1901.23.

- E. Gerami, M. Delshad, M. R. Amini, M. R. Yazdani, "A new family of non-isolated PWM DC-DC converter with soft switching," IET Power Electronics, 12(2), (2019), 237-244,.

- T. Meng, H. Ben, X. Wang, A passive flyback auxiliary circuit with integrated transformer suitable for three-phase isolated full-bridge boost PFC converter, IEEE Trans. Power Electron. 31 (2016) 4995–5003. https://doi.org/10.1109/TPEL.2015.2477493.

- C.-C. Hua, Y.-H. Fang, C.-H. Huang, Zero-voltage-transition bridgeless power factor correction rectifier with soft–switched auxiliary circuit, IET Power Electron. 9 (2016) 546–552. https://doi.org/10.1049/iet-pel.2015.0345.

- M.R. Yazdani, H. Farzanehfard, J. Faiz, EMI analysis and evaluation of an improved ZCT flyback converter, IEEE Trans. Power Electron. 26 (2011) 2326–2334. https://doi.org/10.1109/TPEL.2010.2098363.

- K.-H. Chao, M.-S. Yang, High step-up interleaved converter with soft-switching using a single auxiliary switch for a fuel cell system, IET Power Electron. 7 (2014) 2704–2716. https://doi.org/10.1049/iet-pel.2013.0715.

- Ahmed, N., Araf, A., Rakeen, S. A Multi-Input Single-Ended Primary Inductor Converter (SEPIC): Performance Analysis for Hybrid Sources of Renewable Energy. *Majlesi Journal of Electrical Engineering*, 2024; 18(1): 165–178. doi: 10.30486/mjee.2024.1995734.1247

- H.-T. Yang, J.-T. Liao, X.-Y. Cheng, Zero-voltage-transition auxiliary circuit with dual resonant tank for DC-DC converters with synchronous rectification, IET Power Electron. 6 (2013) 1157–1164. https://doi.org/10.1049/iet-pel.2012.0134.

- G. Yao, A. Chen, X. He, Soft switching circuit for interleaved boost converters, IEEE Trans. Power Electron. 22 (2007) 80–86. https://doi.org/10.1109/TPEL.2006.886620.

- N.J. Park, D.S. Hyun, IBC using a single resonant inductor for high-power applications, IEEE Trans. Ind. Electron. 56 (2009) 1522–1530. https://doi.org/10.1109/TIE.2008.2002676.

- Y.-T. Chen, S.-M. Shiu, R.-H. Liang, Analysis and design of a zero-voltage-switching and zero-current-switching interleaved boost converter, IEEE Trans. Power Electron. 27 (2012) 161–173. https://doi.org/10.1109/TPEL.2011.2151208.

- Y.-T. Chen, Z.-M. Li, R.-H. Liang, A novel soft-switching interleaved coupled-inductor boost converter with only single auxiliary circuit, IEEE Trans. Power Electron. 33 (2018) 2267–2281. https://doi.org/10.1109/TPEL.2017.2703171.

- K.-J. Lee, R.-Y. Kim, D.-S. Hyun, Nonisolated ZVT two-inductor boost converter with a single resonant inductor for high step-up applications, IEEE Trans. Power Electron. 27 (2012) 1966–1973. https://doi.org/10.1109/TPEL.2011.2164094.

- R.T.-H. Li, C.N.-M. Ho, An active snubber cell for N-phase interleaved DC-DC converters, IEEE J. Emerg. Sel. Top. Power Electron. 4 (2016) 344–351. https://doi.org/10.1109/JESTPE.2015.2477999.

- C.-M. Wang, C.-H. Lin, C.-M. Lu, Design and realisation of a zero-voltage transition pulse-width modulation interleaved boost power factor correction converter, IET Power Electron. 8 (2015) 1542–1551. https://doi.org/10.1049/iet-pel.2014.0389. Y.-C. Hsieh, T.-C. Hsueh, H.-C. Yen, An interleaved boost converter with zero-voltage transition, IEEE Trans. Power Electron. 24 (2009) 973–981. https://doi.org/10.1109/TPEL.2008.2008932.

- M. Abbasi, N. Mortazavi, A. Rahmati, A novel ZVS interleaved boost converter, in 5th Power Electron., Drive Syst. Tech. Conf. (PEDSTC 2014), IEEE, 2014, pp. 535–538. https://doi.org/10.1109/PEDSTC.2014.6799425.

- J.-H. Yi, B.-H. Cho, Zero-voltage-transition interleaved boost converter with an auxiliary coupled inductor, IEEE Trans. Power Electron. 32 (2017) 5917–5930. https://doi.org/10.1109/TPEL.2016.2631618.

- M. Esteki, E. Adib, H. Farzanehfard, S.A. Arshadi, Auxiliary circuit for zero-voltage-transition interleaved pulse-width modulation buck converter, IET Power Electron. 9 (2016) 568–575. https://doi.org/10.1049/iet-pel.2015.0515.

- C.S. Moo, Y.J. Chen, H.L. Cheng, Y.C. Hsieh, Twin-buck converter with zero-voltage transition, IEEE Trans. Ind. Electron. 58 (2011) 2366–2371. https://doi.org/10.1109/TIE.2010.2062433.

- E. Maali, B. Vahidi, Double-deck buck-boost converter with soft switching operation, IEEE Trans. Power Electron. 31 (2016) 4324–4330. https://doi.org/10.1109/TPEL.2015.2465894.

- J.P. Gegner, C.Q. Lee, Zero-voltage-transition converters using a simple magnetic feedback technique, in IEEE PESC Conf., IEEE, 1994, pp. 590–596. https://doi.org/10.1109/PESC.1994.349971.

- M. R. Yazdani, H. Farzanehfard, and J. Faiz, `EMI analysis and evaluation of an improved ZCT \_yback converter," IEEE Trans. Power Electron., vol. 26, no. 8, pp. 2326\_2334, Aug. 2011.

- T. Shamsi, M. Delshad, E. Adib, and M. Rouholla, ``Anewsimple-structure passive lossless snubber for DC\_DC boost converters," IEEE Trans. Ind. Electron., vol. 68, no. 3, pp. 2207\_2214, Mar. 2021.

- J. Zeng, W. Qiao, L. Qu, and Y. Jiao, "An isolated multiport DC–DC converter or simultaneous power management of multiple different renewable energy sources," IEEE J. Emerg. Sel. Top. Power Electron., vol. 2, no. 1, pp. 70-78, 2014.

- L. Müller, J.W. Kimball, High gain DC-DC converter based on the Cockcroft-Walton multiplier, IEEE Trans. Power Electron. 31 (2016) 6405-6415. https://doi.org/10.1109/TPEL.2015.2495299.

- V.A.K. Prabhala, P. Fajri, V.S.P. Gouribhatla, et al., A DC–DC converter with high voltage gain and two input boost stages, IEEE Trans. Power Electron. 31 (2016) 4206–4215. https://doi.org/10.1109/TPEL.2015.2467303.

- A. Alzahrani, M. Ferdowsi, P. Shamsi, High-voltage-gain DC–DC step-up converter with bi-fold Dickson voltage multiplier cells, IEEE Trans. Power Electron. 34 (2019) 873–881. https://doi.org/10.1109/TPEL.2018.2890437.

- Y. Tang, T.Wang, and Y. He, "A switched-capacitor-based active-network converter with high voltage gain," IEEE Trans. Power Electron., vol. 29, no. 6, pp. 2959–2968, Jun. 2014.

- Deihimi, A., Mahmoodieh, M.E.S., Iravani, R.: 'A new multi-input step-up DC-DC converter for hybrid energy systems', Electr. Power Syst. Res., 2017, 149, pp. 111–124N.

- kumar Reddi, M. Ramteke, H. Suryawanshi, K. Koteswararao, and S. Gawande, "An Isolated Multi-Input ZCS DC-DC Front-End-Converter Based Multilevel Inverter for the Integration of Renewable Energy Sources," IEEE Trans. Ind. Appl., 2017.

- J. Zeng, W. Qiao, L. Qu, and Y. Jiao, "An isolated multiport DC–DC converter for simultaneous power management of multiple different renewable energy sources," IEEE J. Emerg. Sel. Top. Power Electron., vol. 2, no. 1, pp. 70-78, 2014.

- S. Jalilyan, V. Abbasi, S. Ahmadian, A. R. Varmenjeh and F. Y. Moghadam, "High Step-Up Three-Port DC–DC Converter With Few Limitations in Performance Suitable for Stand-Alone Renewable Energy Applications," in IEEE Transactions on Industrial Electronics, vol. 71, no. 10, pp. 12389-12401, Oct. 2024, doi: 10.1109/TIE.2024.3360616.

- S. Ahmadian, F. Y. Moghadam, V. Abbasi, S. Jalilyan and S. A. Gorji, "A High–Gain and Cost–Effective Three–Port DC-DC Converter with Reduced Semiconductor Stress and Higher Power Density," in IEEE Open Journal of Power Electronics, doi: 10.1109/OJPEL.2025.3557354.

- S. Jalilyan, V. Abbasi, A. Rahimi Varmenjeh, S. Ahmadian and S. A. Gorji, "High Voltage-Gain Common-Ground Three-Port DC-DC Converter With Low Current Ripples on the PV Source for Standalone Applications," in IEEE Access, vol. 12, pp. 80896-80909, 2024, doi: 10.1109/ACCESS.2024.3408639.

- Conve.

Electronics

Record Research Agencies (1984) S. Jalilyan, V. Abbasi, E. Adib, S. A. Gorji and D. Sera, "Soft-Switched Three-Port DC-DC Converter for